The INTCON Register

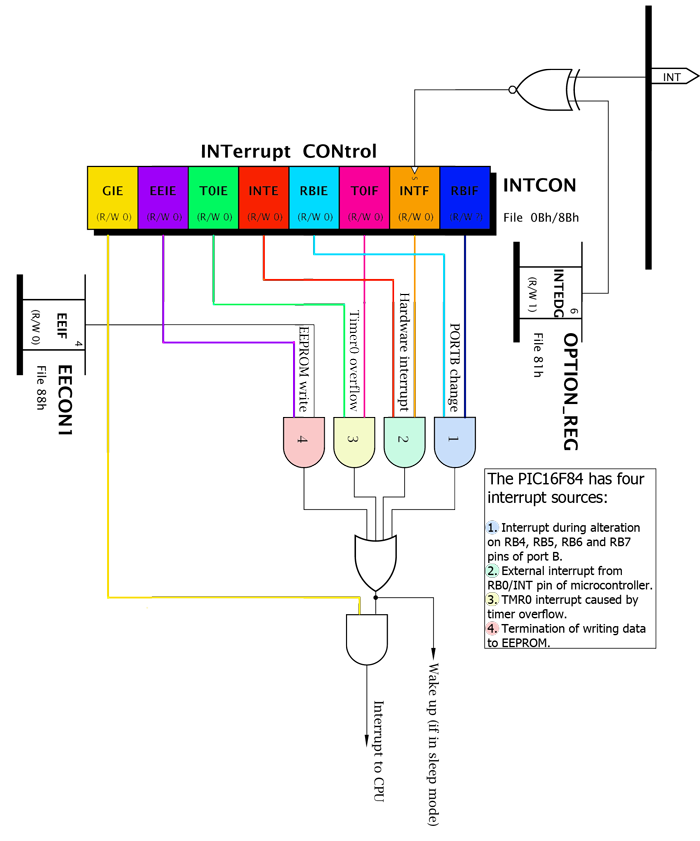

Introduction: The PIC16F84 has four interrupt sources:

Generally speaking, each interrupt source has two bits associated with it. One enables interrupts, and the other detects when interrupts occur. There is one common bit called GIE which can be used to disable or enable all interrupts simultaneously. This bit is very useful when writing a programme because it allows for all interrupts to be disabled for a period of time, so that execution of some important part of a programme would not be interrupted. When the instruction which resets GIE bit is executed (GIE=0, all interrupts disallowed), any interrupt that remained unsolved would be ignored. Interrupts which remained unsolved and were ignored, are processed when GIE bit (GIE=1, all interrupts allowed) would be cleared. When interrupt was answered, GIE bit was cleared so that any additional interrupts would be disabled, return address was pushed onto stack and address 0004h was written in programme counter - only after this does replying to an interrupt begin! After interrupt is processed, the bit which caused an interrupt must be cleared, or the interrupt routine would automatically be processed over again during a return to the main programme.

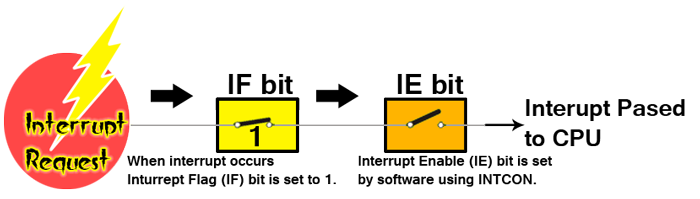

Interrupt Request Mechanism

The INTCON Register:The INTCON register is a readable and writable register which contains the various enable bits for all interrupt sources. The meaning of INTCON might be (though this is only me thinking) INTurrpt CONtrol register. I have serached the net for the source of this acronym with no avail; if you find it please e-mail me. Anyway, interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>).

This register is used to configure the interrupt control logic circuitry. Bits 0 to 6 are used to configure the interrupt enable/disable statuses and the interrupt flags for the four interrupt sources. No interrupt to the CPU will result unless the GIE bit is set. The GIE bit is the bit INTCON<7> and when set, enables all un-masked interrupts.

|

||||||||||||||||||||||||||||||||||||||||||||||||